소개

Xilinx의 Vivado와 함께 Partial Reconfiguration (또는 Dynamic Function eXchange, DFX)에 대한 4개의 시리즈 중 두 번째 게시물입니다. 이 게시물의 의도는 FPGA design에서 Partial Reconfiguration을 활성화하는 단계를 살펴보고 설명하는 것입니다. 아직 읽지 않았다면 첫 번째 게시물 을 읽는 것이 좋습니다. 이 단계의 개념이 설명되어 있기 때문입니다.

Xilinx는 2020에서 Partial Reconfiguration 의 이름을 "Dynamic Function eXchange"(DFX)로 변경했습니다. DFX는 Vivado의 메뉴와 참고 사항에 사용되는 표현입니다. 그럼에도 불구하고 여기에서는 기술 용어 "Partial Reconfiguration"가 사용됩니다.

단순화를 위해 이 게시물은 프로젝트에서 reconfigurable partition을 하나만 가정합니다. 이것을 여러 partitions 로 확장하는 것은 매우 간단합니다.

이 게시물에 설명된 절차는 프로젝트가 Partial Reconfiguration에 대해 활성화 되기 전에 시작됩니다. 따라서 대략적으로 분류하면 다음과 같습니다.

- floorplanning용 프로젝트 준비

- Partial Reconfiguration용 초기 project setup 만들기

- Floorplanning

- design의 implementation 로 floorplanning 확인 및 수정

- 두 번째 reconfigurable module (또는 여러 modules) 추가

- bitstream 파일을 얻으려면 implementation을 수행하십시오.

- 프로젝트 검토

floorplanning준비

다른 어떤 작업보다 floorplanning은 브레인워크가 필요한 작업입니다. FPGA logic 의 영역을 낭비하지 않는 것과 static partition 와 reconfigurable partitions 모두 place and route동안 상당한 장애물이 없도록 하는 것 사이의 미묘한 균형입니다.

따라서 이 게시물의 대부분은 이 주제에 대해 설명합니다.

먼 과거에 floorplanning은 timing closure에 사용되는 기술이었습니다. 도구가 logic을 합리적인 방법으로 배치하는 데 도움이 되었습니다. FPGA design 용 도구가 시간이 지남에 따라 향상됨에 따라 floorplanning이 timing constraints를 달성하는 데 도움이 된 것을 마지막으로 본 지 여러 해가 되었습니다. 오늘날 timing constraints를 달성하기 위한 최선의 전략은 거의 항상 도구가 결정을 내리도록 하는 것입니다.

Partial Reconfiguration에서는 floorplanning이 필수이므로 상황을 악화시키는 것이 목표가 아닙니다. 이렇게 하는 것은 일반적으로 시행착오의 문제입니다. 그러나 좋은 결과를 얻는 가장 간단한 방법은 floorplanning없이 design 의 implementation을 수행한 다음 logic을 자연스럽게 배치하는 방법부터 시작하는 것입니다. 다음 단계는 logic 의 초기 배치를 가이드라인으로 사용하여 Partial Reconfiguration에 적합한 방식으로 영역을 구성하는 것입니다.

plugin 사용 시나리오에서 floorplanning은 시간이 지남에 따라 프로젝트가 발전함에 따라 업데이트될 수 있습니다. 그러나 Remote Update 시나리오에서는 그렇지 않습니다. 즉, Partial Reconfiguration이 출시된 design 에 대한 버전 업데이트를 수행하는 수단으로 사용되는 경우: Remote Update에서는 모든 partial bitstreams가 initial bitstream와 일치해야 합니다. 따라서 design 의 static logic 부분은 initial bitstream이 출시되자마자 동결됩니다. 이것은 무엇보다도 floorplanning이 동일하게 유지되어야 함을 의미합니다.

따라서 Partial Reconfiguration을 시작하기 전에도 첫 번째 작업은 static logic용 FPGA 에서 적절한 영역을 찾는 것입니다. 이것에 너무 많은 시간을 낭비할 이유가 없습니다. 프로젝트가 두 부분으로 분할된 후 계속 진행하기 위한 시작점을 얻으십시오.

혼동하지 마십시오: 이 첫 번째 단계의 목적은 floorplanning 자체가 아니라 Vivado가 제한 없이 logic을 배치하는 방법을 확인하고 static logic에 할당할 영역을 결정하는 것입니다. 다음은 단계입니다.

- 평소와 같이 design 의 implementation을 수행합니다. implemented design을 열고 device view를 보십시오. static design이 소비하는 logic 리소스의 양과 Vivado가 이러한 리소스를 선호하는 방식에 대한 아이디어를 얻으십시오.

- reconfigurable logic 로 의도된 부분이 프로젝트에서 일시적으로 제거되면 이 작업을 수행하는 것이 더 쉬울 수 있습니다(그러나 logic optimization로 인해 static logic 도 제거되지 않는 방식).

- Device view에서 logic element가 선택되지 않았는지 확인하고 그 위에 Right-click을 수행하고 "Draw Pblock"를 선택합니다. static logic을 수용하기에 적합해 보이는 영역을 그립니다. 꼭 Vivado가 만든 배치를 모방하지 말고, logic을 배치하고 timing constraints를 달성하는 데 장애물을 만들지 않고 최소한의 영역을 할당하는 모양을 찾아보십시오.

- Vivado는 "Create a new Pblock"라는 대화 상자를 열어 응답합니다. Pblock을 clock regions로 정의하는 것이 좋습니다. 그렇다면 하지 마십시오. slices, DSPs 및 기타 logic elements를 기반으로 Pblock을 요청하십시오.

- Ultrascale FPGAs의 경우 Pblock 대화 상자에서 IOBs를 포함하도록 제안할 수도 있습니다. 그렇다면 해당 옵션을 선택 해제하십시오. 그렇지 않으면 나중에 Pblock을 저장하거나 크기를 조정하는 동안 Vivado가 멈출 수 있습니다( Vivado의 버그로 인해).

- Pblock의 모양, 특히 slices의 범위에 주의하십시오. 이 정보는 Vivado의 GUI ("General" 탭 아래)의 Pblock properties pane 또는 다음과 같은 내용이 기록되는 Tcl Console에서 얻을 수 있습니다.

startgroup create_pblock pblock_1 resize_pblock pblock_1 -add {SLICE_X108Y148:SLICE_X149Y249 DSP48_X4Y60:DSP48_X5Y99 RAMB18_X4Y60:RAMB18_X6Y99 RAMB36_X4Y30:RAMB36_X6Y49} endgroup - Tcl Console에 warnings가 있으면 무시하십시오.

- implemented design을 닫을 때 Vivado는 저장 여부를 묻습니다. 방금 만든 Pblock은 사용하지 않으므로 "No"를 선택합니다.

Partial Reconfiguration용 프로젝트 설정

Xilinx의 UG909 는 Partial Reconfiguration에 대한 두 가지 작업 절차를 제안합니다.

- non-project flow (3장에서), 이는 implementation이 Tcl scripts를 명시적으로 작성하고 실행하여 수행됨을 의미합니다.

- project flow (4장)는 Vivado의 GUI 와 scripts 에 의해 자동으로 생성되는 사용에 해당합니다.

여기서는 project flow를 사용하겠습니다. 몇 가지 제한 사항이 있지만 그 중 일부는 reconfigurable module 의 sources 유형과 관련이 있습니다(특히 block designs사용과 관련하여). 어느 쪽이든, implementation 용으로 생성하는 scripts는 필요한 경우 non-project flow의 좋은 기반이기 때문에 project flow로 시작하는 것이 좋습니다.

기존 프로젝트에서 Partial Reconfiguration 지원을 켜는 단계는 다음과 같습니다.

- Tools > Enable Dynamic Function eXchange…를 선택하고 "Convert"를 클릭합니다. GUI는 프로젝트를 Partial Reconfigurable flow 로 전환하는 것은 되돌릴 수 없음을 알고 있으므로 이에 동의합니다. 실제로 실행되는 Tcl 명령은 다음과 같습니다.

set_property PR_FLOW 1 [current_project]

- reconfigurable partition용 top level module을 결정하고 Vivado에서 Project Manager의 Sources pane 아래에 있는 source file을 마우스 오른쪽 버튼으로 클릭합니다. "Create Partition Definition…"를 선택하십시오. 이 옵션은 DFX를 활성화한 후에만 사용할 수 있지만 방금 수행했습니다.

- 두 가지를 묻는 "Create Partition Definition" 대화 상자 창이 나타납니다. logic의 계층 구조를 참조하는 데 사용되는 Partition Definition의 이름입니다. 이 이름은 계층 구조에서 다른 reconfigurable modules를 삽입할 수 있는 위치를 나타냅니다. 적절한 이름은 "pr"일 수 있습니다. 두 번째 항목인 Reconfigurable Module Name은 어떤 logic이 partition에 들어가는지 알려줍니다. 예를 들어 Partial Configuration이 audio filter를 대체하는 데 사용되는 경우 Reconfigurable Module Name 에 대한 합리적인 선택은 "lpf", "bpf", "hpf"가 될 수 있으므로 각 이름에는 적용되는 필터가 표시됩니다. 그것이하는 일을 이해하는 데 도움이된다면 top-level module의 이름이 될 수 있습니다.

- Sources list 에서 선택한 module 의 행은 이제 Verilog / VHDL 파일에 정의된 대로 module 및 instance name (예: "pr_block" 및 "pr_block_ins")의 이름과 함께 노란색 다이아몬드 모양으로 나타납니다. 이 이름은 어떤 logic이 partition에 삽입되었는지에 대해 아무 말도 하지 않고 오히려 HDL에 해당 이름을 반영합니다. partition 및 reconfigurable module은 동일한 Sources pane의 "Partition Definitions" 탭에서 찾을 수 있습니다.

- IP 의 instantiations가 있는 경우(예: reconfigurable module의 FIFO) , IP는 기본 프로젝트의 sources ("Hierarchy" 창 아래)에서 해당 행을 마우스 오른쪽 버튼으로 클릭하고 "Move to configurable module…"를 선택하여 추가할 수 있습니다. Tcl 의 해당 항목은 다음과 같습니다. 다음과 같은 것:

move_files -of_objects [get_reconfig_modules lpf] [get_files /path/to/blkmem.xci]이렇게 하면 IP가 "Partition Definitions" 탭으로 이동합니다. - 뿐만 아니라 "Partition Definitions" 탭은 각 reconfigurable module에 대한 source hierarchies 모음처럼 작동합니다. 예를 들어, reconfigurable module에 필요한 HDL 파일을 추가하려면 이 탭에서 "+"를 클릭하십시오.

- reconfigurable module이 설정되면 Parent Implementation을 정의하십시오( Parent implementations, Child implementations 및 Wizard에 대한 이전 게시물 참조):

- Tools > Dynamic Function eXchange Wizard를 선택합니다.

- 환영 페이지와 reconfigurable modules편집 페이지에서 Next를 클릭합니다.

- "Edit Configurations" 페이지에서 "+"를 클릭하여 configuration을 추가합니다. 기본 config_1 이름은 그다지 중요하지 않으므로 괜찮습니다. 기본적으로 Vivado는 config_1에 대해 reconfigurable module을 올바르게 선택합니다. 현재로서는 reconfigurable module이 유일하기 때문에 놀라운 일이 아닙니다.

- 다음 화면은 configuration runs를 추가하는 화면입니다. (지금은) 이것을 하지 마십시오.

- Wizard를 마칩니다.

이 단계에서 프로젝트의 implementation을 수행하려고 하면 "[DRC HDPR-30] Missing PBLOCK On Reconfigurable Cell: HD.RECONFIGURABLE cell 'pr_block_ins' must have PBLOCK assigned to itself or its descendant cells"와 같은 오류와 함께 실패할 가능성이 큽니다. 즉, 간단히 말해서 floorplanning이 필요하다는 것입니다.

Floorplanning

이 단계에서 프로젝트는 floorplanning 작업에 충분하도록 설정됩니다.

이 작업을 작은 단계로 나누기 전에 염두에 두어야 할 몇 가지 사항을 언급할 가치가 있습니다.

- static logic 의 경우 FPGA 의 영역은 가능한 한 작게 만들어야 하지만 place and route에 대해 어렵게 만들지 않아야 합니다. 모양에 대한 대략적인 평가는 이전에 얻어야 합니다(위의 "Preparation for floorplanning" 참조).

- static logic 및 reconfigurable logic 의 모양은 가능한 한 단순해야 하며, routing에 어려움을 일으키지 않는 일반 직사각형 또는 기타 모양이 바람직합니다.

- static logic의 routing은 reconfigurable logic의 영역을 넘을 수 있지만 그 반대는 대부분의 경우 사실이 아닙니다.

- 이 floorplanning 세션에서는 reconfigurable logic 의 모양이 그려집니다. 마지막 두 개의 주석으로 인해 이것은 단순하게 유지하는 모양입니다.

- UG909의 6-8 장에 자세히 설명된 대로 특정 FPGA의 floorplanning 와 관련된 가능성과 제한 사항을 알고 있어야 합니다. 예를 들어, series-7 FPGA를 사용하는 경우 영역의 한계를 clock regions의 경계에 맞추는 것이 가장 좋습니다.

이제 단계로 나눕니다.

- 프로젝트의 synthesis를 시작합니다(즉, synth_1 run시작). reconfigurable module 의 synthesis는 자동으로 Out-of-Context run (OOC)로 수행됩니다(예: lpf_synth_1). OOCs는 지난 포스트 에서 자세히 설명합니다.

- runs가 완료되면 synthesized design을 엽니다( reconfigurable module와 연결된 Pblock이 없기 때문에 이 시점에서implementation은 불가능합니다).

- reconfigurable logic에 대해 Pblock을 그립니다. 준비 단계와 달리 reconfigurable logic와 연결되어야 하므로 다음과 같습니다. 왼쪽 상단 pane이 Netlist tab에서 열려 있는지 확인하고 reconfigurable partition 로 들어가는 toplevel cell을 마우스 오른쪽 버튼으로 클릭합니다(예: "pr_block_ins"). Floorplanning > Draw Pblock을 선택하고 FPGA에 영역을 그립니다. 수행할 GUI 작업은 위에서 설명한 바와 같습니다("Preparation for floorplanning" 참조). 즉, 선택은 slices 및 기타 logic elements를 기준으로 합니다.

- 다시 한 번, IOBs가 Pblock에 포함되도록 제안된 경우 이 제안을 수락하지 마십시오. 그렇지 않으면 Vivado가 나중에 처리하는 데 중단될 가능성이 있습니다.

- 이에 대한 Vivado의 불만으로 인해 수정해야 할 가능성이 높으므로 이에 대해 너무 열심히 일하지 마십시오. 다시 한 번, Pblock은 reconfigurable logic에 대해 그려지고 static logic은 나머지 영역을 차지한다는 점을 명심하십시오.

- 이제 Pblock Properties pane로 이동합니다. device view에서 Pblock을 마우스 오른쪽 버튼으로 클릭하고 Pblock Properties…를 선택해야 표시될 수 있습니다.

- Properties tab을 선택합니다( Pblock Properties pane에서).

- series-7 FPGAs 의 경우(즉, Ultrascale 이상 아님): Pblock Properties pane에서 partial bitstream을 로드한 후 logic이 FPGA의 내부 reset을 가져오도록 하려면 RESET_AFTER_RECONFIG을 설정하는 것이 좋습니다( reconfigurable module재설정에 대한 자세한 내용은 다음 게시물 참조). 그러면 다음과 같은 XDC constraint가 생성됩니다.

set_property RESET_AFTER_RECONFIG true [get_pblocks pblock_pr_block_ins]

무엇보다도 이 constraint는 flip-flops를 기본값으로 가져옵니다. 그러나 이것은 HDL 또는 logic에 정의된 resets 와 아무 관련이 없습니다. 또한 series-7 FPGAs에서 이 기능을 사용하려면 Pblock의 수직 경계가 clock regions와 정렬되어야 합니다.

Ultrascale FPGAs 이상에서 이 reset은 항상 활성화되어 있습니다. - series-7 FPGAs 에 대해 기본적으로 정의되지 않은 SNAPPING_MODE 속성도 있습니다( OFF와 동일). 일부 FPGAs의 경우 ROUTING 또는 ON ( Ultrascale의 기본값)로 설정해야 할 수도 있습니다. 나는 나중에 그것에 올 것이다.

- 그런 다음 CTRL-S를 눌러 constraints를 저장합니다(또는 상단 표시줄에서 디스켓 아이콘 클릭). 그러면 다음과 같이 XDC 파일에 몇 개의 행이 추가됩니다.

create_pblock pblock_pr_block_ins add_cells_to_pblock [get_pblocks pblock_pr_block_ins] [get_cells -quiet [list pr_block_ins]] resize_pblock [get_pblocks pblock_pr_block_ins] -add {SLICE_X40Y100:SLICE_X79Y149} resize_pblock [get_pblocks pblock_pr_block_ins] -add {DSP48_X2Y40:DSP48_X2Y59} resize_pblock [get_pblocks pblock_pr_block_ins] -add {RAMB18_X2Y40:RAMB18_X2Y59} resize_pblock [get_pblocks pblock_pr_block_ins] -add {RAMB36_X2Y20:RAMB36_X2Y29} - Synthesized Design닫기

- synth_1 run을 재설정합니다.

- bitstream생성을 시도합니다 ("Generate Bitstream" 클릭). 이 implementation 의 목적은 floorplanning에 결함이 있는지 확인하는 것입니다. 즉, Vivado가 이러한 결함에 대응하여 Critical Warnings를 발행한다면. design을 검증하는 비전문적인 방법처럼 들릴 수 있지만 쉽고 안정적입니다.

floorplanning수정

이것은 아마도 Partial Reconfiguration에서 가장 유쾌하지 않은 부분일 것입니다. floorplanning을 바로 사용하려면. Remote Update 사용 사례에 대해 이 작업을 수행하는 경우 이 floorplanning이 프로젝트 수명 내내 유지되므로 이 단계가 더욱 중요합니다.

floorplanning 에 대한 수정은 두 가지 주요 이유로 필요합니다. Critical Warnings에 대한 응답으로, 그리고 이후 단계에서 FPGA사용을 최적화하기 위해: 목표는 자원 낭비를 줄이는 동시에 place and route에 대한 장애물 생성을 피하는 것입니다.

Pblock의 경계를 드래그하기 쉽기 때문에 수정하는 것은 어렵지 않습니다. 또한 추가 직사각형으로 Pblock을 쉽게 확장할 수 있습니다. Pblock을 마우스 오른쪽 버튼으로 클릭하고 "Add Pblock Rectangle"를 선택합니다.

Critical Warnings는 종종 어떤 수정이 필요하다고 말하지만 특정 FPGA의 floorplanning 에 대한 제한 사항에 대해 Xilinx사용자 가이드 UG909 의 관련 장(6, 7 또는 8)을 반드시 읽어야 합니다.

이 섹션의 나머지 부분에서는 series-7 FPGA에서 발생할 수 있는 문제에 대해 설명합니다. Ultrascale FPGAs는 작업하기가 훨씬 쉽습니다.

series-7 FPGA 의 일반적인 오류 중 하나는 interconnect tile columns의 분할입니다. 예를 들면 다음과 같습니다.

[Constraints 18-993] The Pblock pblock_pr_block_ins has defined an area that causes the splitting of interconnect tile columns. Dynamic Function eXchange requires that the left and right paired interconnect tile columns cannot be split by a reconfigurable boundary. This is caused by either the left or right edge of a Pblock boundary, or by the Pblock spanning over logic types not included in the Pblock ranges. To avoid an unroutable situation, placement will be prohibited from both of these columns. To avoid placement restrictions, modify the Pblock to avoid splitting the two columns. The column of the split contains interconnect tile INT_L_X48Y299 (SLICE_X79Y299 SLICE_X78Y299). Please refer to the Xilinx document on Dynamic Function eXchange. Resolution: Set the Pblock property SNAPPING_MODE to value of ON, or modify the column/X specification of the pblock to avoid this edge.

그리고

[Constraints 18-996] The split between the left and right columns occurs between a reconfigurable Pblock and Static logic. The static sites are not reconfigurable. The Pblock should be adjusted to remove the column from the Pblock, unless the excluded reconfigurable and static sites are not needed for the design. Note that adjusting the Pblock will prevent prohibits and improve placement of the design, but may reduce the routability if the removed sites were needed to span across the static logic. Failure to modify the Pblock may lead to an unplaceable design if these prohibited sites are required by the design. Resolution: Set the Pblock property SNAPPING_MODE to value of ON, or modify the column/X specification of the pblock to avoid this edge. and

이 문제를 해결하려면 첫 번째 warning에서 제안한 대로 Pblock의 SNAPPING_MODE 속성을 ROUTING 또는 ON 로 설정합니다( ROUTING 로는 충분하지 않으므로 ON선택). 이렇게 하면 다음과 같은 XDC 파일에 많은 constraints가 추가될 것입니다.

set_property PROHIBIT true [get_sites SLICE_X79Y349] set_property PROHIBIT true [get_sites SLICE_X78Y349] [ ... ] set_property PROHIBIT true [get_sites SLICE_X79Y191] set_property PROHIBIT true [get_sites SLICE_X78Y191] set_property PROHIBIT true [get_sites PMV_X0Y2] set_property PROHIBIT true [get_sites SLICE_X36Y190] set_property PROHIBIT true [get_sites SLICE_X37Y190] [ ... ] set_property PROHIBIT true [get_sites SLICE_X79Y176] set_property PROHIBIT true [get_sites SLICE_X78Y176] set_property PROHIBIT true [get_sites T14] set_property PROHIBIT true [get_sites R15] set_property PROHIBIT true [get_sites XADC_X0Y0] set_property PROHIBIT true [get_sites SLICE_X36Y175] set_property PROHIBIT true [get_sites SLICE_X37Y175] [ ... ]

그리고 계속됩니다.

slice 사이트에 대한 PROHIBIT 설정은 해당 Critical Warning을 침묵시키는 설정입니다. 다른 PROHIBIT 할당은 기하학적 영역에 포함된 logic 사이트에 추가되지만 사용되는 FPGA 의 Partial Reconfiguration 에는 허용되지 않습니다. Ultrascale FPGAs 이상에서는 PROHIBIT이 있는 경우 훨씬 적은 행을 생성합니다.

Critical Warning을 침묵시킬 목적으로 PROHIBIT로 모든 행을 제거하고 slices 에 대해서만 하나의 단일 행을 남겨두는 것이 좋습니다. 이는 SNAPPING_MODE의 변경에 따라 Vivado가 추가한 slices 의 범위를 커버함으로써 이루어집니다. 따라서 이 범위를 다음과 같이 바꾸십시오.

set_property PROHIBIT true [get_sites -range {SLICE_X79Y0 SLICE_X79Y349}]

이것은 파일을 크게 만들지 않고 interconnect splitting 의 문제를 해결할 수 있는 XDC 파일의 행 종류입니다.

그럼에도 불구하고 이러한 종류의 행은 XDC 파일에도 나타날 수 있습니다. 이 행을 제거하는 것도 분명히 괜찮습니다.

set_property HD.PLATFORM_WRAPPER true [get_cells pr_block_ins]

XDC 파일을 Critical Warnings를 침묵시키는 최소로 줄이는 것은 다소 피상적으로 보일 수 있지만, 대안은 나중에 혼동을 일으킬 수 있는 거대한 constraints 파일입니다. 내 경험상 이런 종류의 warnings가 없다는 것은 design의 floorplan이 괜찮다는 승인으로 받아들여질 수 있습니다.

SNAPPING_MODE 속성을 OFF 로 되돌리면 XDC의 변경 사항에 관계없이 다시 문제가 발생할 가능성이 있습니다.

reconfigurable module추가

지금까지 implementation은 몇 가지 추가 제한 사항을 제외하고는 실질적으로 hierarchical design와 동일한 성능을 제공합니다. partial bitstream이 생성되더라도 로드하면 동일한 design을 유지하므로 거의 쓸모가 없습니다.

따라서 목표는 다른 configurable module을 기반으로 하는 또 다른 partial bitstream을 만드는 것입니다. 이를 위해서는 Child Implementation을 추가해야 합니다.

이 글을 읽기 전에 이전 포스트 , 특히 Parent Implementations 와 Child Implementations, 그리고 Dynamic Function eXchange Wizard에 대한 부분을 염두에 두십시오. 또한 이 게시물의 위에서 "Partition Definitions" 탭에는 현재 정의된 reconfigurable modules 및 해당 sources가 포함되어 있습니다.

Tools 메뉴에서 Dynamic Function eXchange Wizard를 열고 시작 창에서 Next를 클릭합니다.

Edit Reconfigurable Modules 창에서 "+"를 클릭합니다. 그러면 reconfigurable module을 추가하기 위한 dialog box가 열립니다. 이 dialog box 의 유일한 흥미로운 점은 Reconfigurable Module Name입니다. 이것은 이미 위에서 설명한 대로 reconfigurable logic을 식별하는 데 사용되는 이름입니다.

대화 상자는 또한 이 module을 partition definition의 이름과 연결해야 하지만, 어쨌든 그런 것은 하나만 있습니다(이 게시물에서는 partition이 하나만 정의되어 있다고 가정하기 때문입니다).

계속하려면 하나 이상의 Verilog / VHDL source file을 추가해야 합니다. 나중에 "Partition Definitions" 탭에서 더 많은 것을 추가할 수 있습니다. 특히 source 파일 자체에서 명확하지 않은 경우 이 reconfigurable module 의 toplevel module 이름을 추가해도 문제가 되지 않습니다.

Wizard로 돌아가서 Next를 다시 클릭하여 Edit Configurations 창으로 이동합니다. "+"를 클릭하고 configuration 이름을 입력합니다. 이 이름의 유일한 중요성은 Design Runs 창에 표시된다는 것입니다. config_2 정도의 이름이 좋습니다.

configurations목록에 새 행이 나타납니다. partition열에서 configurable module을 수정하여 각 configuration이 다른 configurable module을 갖도록 합니다.

마지막 창은 runs를 configurations에 할당하기 위한 Edit Configuration Runs입니다. 쉬운 방법은 이 창(있는 경우)에 나열된 모든 runs를 삭제하고 "automatically create configuration runs"를 클릭하는 것입니다. 어쨌든 수동으로 수행하는 작업을 수행합니다. parent run을 만들고 "impl_1"라고 하고 child runs를 만들고 원하는 대로 부르고 "impl_1"의 children 로 만듭니다.

Wizard는 각 run에 대해 configuration을 선택하지만 변경하기 쉽습니다. 유일한 중요한 것은 configuration이 parent run와 연관되어 있다는 것입니다.

그런데 Wizard에서 모든 runs를 삭제하면 모든 child runs는 사라지지만 impl_1은 남습니다.

드디어: design의 Implementation

bitstreams를 생성하려면 평소와 같이 Vivado 에서 "Generate Bitstreams"를 클릭하십시오. 이전 게시물 에서 이미 언급했듯이 Partial Reconfiguration 프로젝트의 각 configuration 에 대해 2개 또는 3개의 bitstreams가 생성됩니다.

예를 들어 Ultrascale FPGA 에서 bitfiles는 다음과 같을 수 있습니다.

- theproject.bit: 현재 configuration와 관련된 static logic 및 configurable logic을 포함하는 initial bitstream 파일입니다.

- pr_block_ins_lpf_partial.bit: 현재 configuration와 관련된 reconfigurable logic을 로드하는 partial bitstream 입니다.

- Ultrascale에만 pr_block_ins_lpf_partial_clear.bit이 있습니다. 현재 configuration이 이미 FPGA에 있는 경우 partial bitstream을 로드하기 전에 로드할 bitstream 입니다.

모든 implementations에 대해 동일한 수의 bitstream 파일이 생성됩니다. 즉, initial bitstream 파일은 Child Implementations 용으로도 생성되므로 Child Implementations의 initial bitstream중 하나와 함께 FPGA를 로드하고 거기에서 계속하는 것이 완벽하게 가능합니다.

PCIe 또는 USB 3.x를 통해 partial bitstreams를 로드하는 간단한 방법은 이 페이지 를 참조하십시오.

implementations 중 어느 것도 Critical Warnings를 가지고 있어서는 안 되며 일반적으로 Pblock 와 floorplanning 에 대한 불만이 있기 때문에 실패하거나 그런 문제는 이미 해결되었을 것이기 때문입니다. 이와 같은 문제가 계속 발생하면 위에서 설명한 대로 floorplanning을 수정해야 합니다.

때때로 "Generate Bitstream"를 클릭하고 child implementations만 변경하면 Vivado가 "Bitstream generation has already completed and is up-to-date. Re-run anyway?"로 응답할 수 있습니다. 이것은 다소 혼란스럽지만 "Yes"를 클릭하면 child implementations가 제대로 실행됩니다. Child Implementation 의 이 모든 것은 Vivado에 대한 약간의 추가 기능이며, 이것이 implementation 동안 status 행이 "write_bitstream complete. Child running"와 같은 것을 말하는 이유이기도 합니다.

결과 검토

Partial Reconfiguration은 배치에 관한 것이므로 implemented designs를 검토하는 것이 좋습니다. "Open Implemented Design"를 마우스 오른쪽 버튼으로 클릭한 다음 "Open Implemented Design"(다시)라는 메뉴 항목 위로 마우스를 가져가 특정 implementation을 열 수 있습니다. 그런 다음 목록에서 열 implementation을 선택하십시오. 목록에 implementation이 없으면 이미 열려 있을 수 있습니다.

Implemented Design 보기의 Netlist pane 에서 reconfigurable logic 의 맨 위 행을 마우스 오른쪽 버튼으로 클릭하고 "Highlight Leaf cells"를 선택하십시오. 그런 다음 다른 색상으로 static logic와 동일한 작업을 수행합니다.

같은 오른쪽 클릭으로 연결된 logic elements 사이에 흰색 직선을 그리는 "Show Connectivity"도 있습니다. FPGA 의 실제 routing paths는 물론 다르므로 이 선이 교차하는 floorplanning 영역은 중요하지 않습니다. 그럼에도 불구하고 연결성을 살펴보면 floorplan 의 전체 구성이 도구에 어려움을 겪을 때를 파악하는 데 도움이 될 수 있습니다.

static logic 에 속하는 것으로 보이는 일부 cells가 reconfigurable area 내부에 배치되고 그 반대의 경우도 마찬가지입니다. 주의해야 할 점은 어딘가에 정체가 있는 것처럼 보이는 경우입니다. logic이 일반적으로 또는 특정 지역에서 너무 꽉 차 있는 것처럼 보이는 경우입니다. 가능하다면 floorplanning을 변경하면 이를 완화하는 데 도움이 될 수 있습니다.

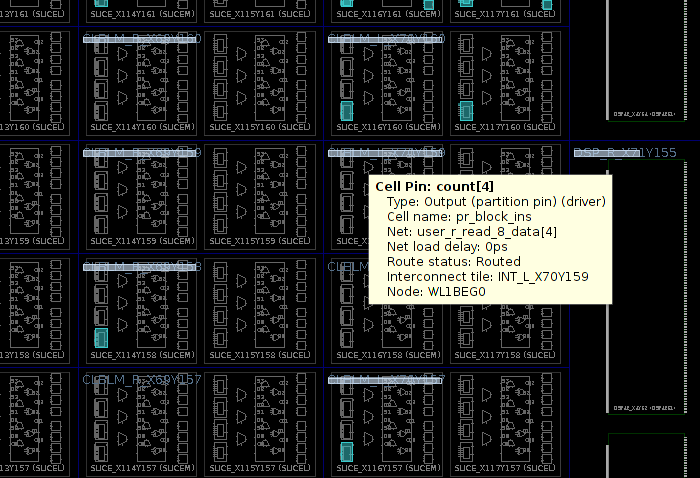

또 하나 살펴볼 것은 partition pins의 위치입니다. 다음과 같이 device view에서 흰색 가로 막대로 나타납니다(확대하려면 이미지를 클릭하십시오).

이전 포스트 에서 언급했듯이 partition pins는 reconfigurable partition내부 어디에나 있을 수 있습니다. 그러나 partition pins가 partition의 가장자리에서 떨어져 있으면 router가 Parent Implementation동안 timing 와 씨름했음을 나타낼 수 있습니다.

이 Tcl 명령을 사용하여 partition pin좌표의 텍스트 목록을 얻을 수도 있습니다( pr_block_ins를 reconfigurable logic cell의 이름으로 변경).

foreach s [get_pins -of [get_cells pr_block_ins]] { set partpin [get_pplocs -quiet -pins [get_pins $s]] ; puts "$s => $partpin"; }

Partition pins 의 좌표는 CLBs 의 그리드에 해당합니다( slices아님). 표시된 도면에서 이러한 핀을 "Cell pins"라고 합니다.

cell의 일부 pins 에는 partition pin이 할당되지 않을 수 있습니다. 이것은 reconfigurable module의 port list (및/또는 vectors의 너비)와 static logic module의 instantiation 사이에 불일치가 있을 때 발생합니다. 이러한 불일치는 완벽하게 합법적이지만( Verilog에서) 결과는 바람직하지 않을 수 있습니다. 이 Tcl 명령을 실행하면 특히 의도하지 않은 경우 연결할 수 없는 ports를 감지할 수 있습니다.

이것으로 Vivado 프로젝트 설정에 대한 기술적인 부분을 마치지만 다음 게시물에서는 FPGA design의 중요한 측면인 logic 의 교체가 안정적이고 원활하게 진행되도록 하는 방법에 대해 설명합니다.