此页面属于关于时序(timing)的一系列页面。前几页解释了时序计算背后的理论,展示了如何编写几个时序约束(timing constraints)并讨论了时序收敛(timing closure)的原理。本页开始讨论 I/O 时序约束。

介绍

到目前为止,关于时序约束(timing constraints)的整个讨论都与 FPGA内部的路径(paths)有关。终于要说到控制 FPGA的 I/O 端口的时序的约束(constraints)了。

但在谈论时序约束之前,有必要了解 FPGA 与外部组件之间同步的不同方法。不考虑这个话题而写的时序约束可能毫无价值。此外,负责 I/O 接口的逻辑可能写得不够好。在极端情况下,电路板可能缺少必要的接线来保证 I/O 正常工作。

了解与外部组件同步的必要性后,可以为时序约束选择正确的命令。下一页将介绍实际方面的内容。

在此页面上,我假设您熟悉IOB 寄存器 。

时钟 distribution(Clock distribution)

只要路径在 FPGA内部,就不需要注意路径两侧之间的时钟偏移(clock skew): 这些工具负责分配时钟,而时序计算将时钟偏移考虑在内。

使用 I/O 时序约束,它是不同的: 路径的一侧是 FPGA之外的外部元件。为了与数据信号(data signals)同步,该组件依赖于它在其中一个引脚上接收到的时钟。但是这个时钟同步的是什么?

该策略通常是以下两者之一:

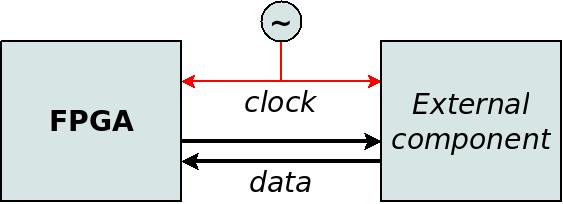

- System synchronous 时钟: 外部组件连接到与 FPGA的时钟输入引脚(clock input pin)相同的时钟信号。此策略也称为 common 时钟。

- Source-synchronous 时钟: 一个特殊的时钟信号与数据信号一起提供。通常数据信号与时钟同时改变值: 使用上升沿(rising edge)或下降沿(falling edge)。

接下来将更详细地讨论这两种策略。关于 source-synchronous 时钟选项,如果数据信号是输入和输出(outputs),则有明显的区别。因此,这些情况将单独讨论。

System synchronous 时钟

在电路板上同步多个组件的最简单方法是将所有组件连接到一个时钟。这称为system synchronous 时钟 (或common clock )。

这种方法的优点是所有组件的时序参数(timing parameters)都相对于一个时钟信号。因此,为了进行时序计算,两侧的时钟相同。因此,对于在电路板上的两个组件之间传播的数据信号,计算类似于 FPGA内的路径: 路径以相对于第一个时钟边沿(clock edge)的 clock-to-output 开头。在路径的末端, tsu 是相对于第二个时钟边沿而言的。 system synchronous 方式就是说这两个时钟边沿属于同一个时钟。

因此,使用 system synchronous 时钟很简单,但是这种方法仅适用于相对较低的频率。回想一下时序计算的介绍,最小的时钟周期(clock period)是几个时序参数(timing parameters)的总和: 第一个触发器(flip-flop)的 clock-to-output ,第二个触发器的传播延迟(propagation delay)和 tsu 。对于输出端口(output port), clock-to-output 相对较大,因为这是电路板的电线达到所需电压所需的时间。但它并没有就此结束: 时钟偏移和与时钟相关的其他不确定性也必须添加。总结所有数字,最小的时钟周期可能不会令人印象深刻。

根据经验, system synchronous 时钟不适用于 I/O ,因为传输速率(data rate)高于 100 MHz。但这在很大程度上取决于涉及哪些组件。事实上,一些电子组件具有时序要求,而 system synchronous 时钟甚至更低的频率都很难满足这些要求。这些组件是为什么在制造电路板之前规划 I/O 时序很重要的原因之一。

set_input_delay 和 set_output_delay (将在下一页说明)是最适合与 system synchronous 时钟一起使用的时序约束。

Source-synchronous 时钟

通常,电路板上两个组件之间的接口基于由其中一个组件提供的时钟。当然,如果时钟是由 FPGA 或外部组件生成,则有所不同。

因此有四种相关情况:

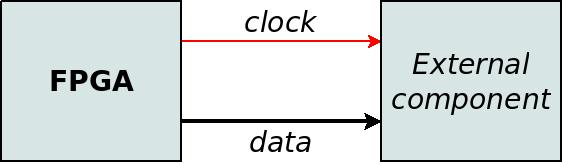

- 数据(data)和时钟是由 FPGA生成的输出。这个相对简单的场景在关于source-synchronous 输出的页面上单独讨论。

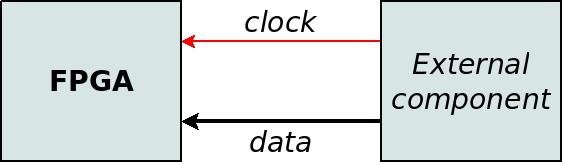

- 数据和时钟由外部组件生成。因此 FPGA 接收这些作为输入信号。关于 source-synchronous inputs 的页面专门针对这种情况。

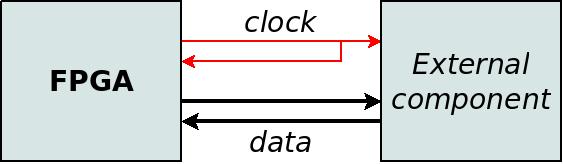

- 时钟由 FPGA生成,但数据是双向的(或输入)。这是 source-synchronous inputs的特例。 FPGA 生成时钟的事实并没有太大的区别: 数据输入(data inputs)与电路板上的时钟同步。这个时钟有一个时延(delay)相对于 FPGA内部的时钟。有关此场景的更多信息,请参阅有关source-synchronous 输出的页面。

- 时钟由外部元件产生,数据是双向的。关于输入到 FPGA,这类似于数据由外部组件(source-synchronous 时钟)生成的场景。至于 FPGA的输出,它们的行为就像任何与外部时钟同步的输出。因此,这些输出的排列方式就好像它们是 system synchronous一样。

异步输入

某些输入与时钟无关。例如,来自外部组件的按钮、 I2C、 RS232 和各种 status 信号与时钟不同步。这些信号通常比 FPGA内部的时钟慢得多。因此,通常的解决方案是使用触发器(flip-flops)(最好是IOB 寄存器 )对这些信号进行采样,然后继续使用常规的逻辑设计技术。

这些输入与用于采样的时钟不同步。因此, IOB 寄存器(或连接到端口的触发器)扮演metastability guards的角色。因此,应为每个端口使用第二个寄存器(register),类似于 unrelated 时钟之间的跨时钟域(clock domain crossing) 。否则,即使输入信号运行缓慢而设计目前似乎工作正常,也存在不可预测和奇怪行为的风险。

应该编写时序约束以确保可重复的行为: 即使触发器未放置在 IOB内,也应遵循与IOB 寄存器相同的指导原则。为了更加安全,最好还添加一个专用的时序约束,以与这些寄存器(registers)的角色相关联,作为 metastability guards (这在另一个页面上解释)。

False paths

I/O 端口的False paths 原则上与 FPGA内部的路径相同: set_false_path 命令用于请求不对特定的端口强制执行任何时序要求。

关于 FPGA内部的路径,已经讨论了False paths 。基于同样的道理, false paths 背后的动机 I/O 端口主要是维护一个空的 unconstrained paths列表。此列表应为空,以便更容易识别端口由于错误而缺少时序约束。

False paths 应该只有在端口的时序完全没有意义的情况下才可以使用。例如,使用 LEDs 和 DIP switches。

SDC 约束的例子:

set_false_path -to [get_ports led_0] set_false_path -from [get_ports dip_switch_0]

概括

此页面概述了一些在 FPGA 和外部组件之间进行同步的策略。选择的策略对逻辑设计和时序约束都有影响。

有了这些知识,就该讨论如何编写 I/O timing constraints了。