このページは、 timingに関する一連のページに属しています。前のページでは、 timing 計算の背後にある理論を説明し、いくつかの timing constraints を記述する方法を示し、 timing closureの原理について説明しました。このページは、 I/O timing constraintsに関する議論を開始します。

序章

この時点まで、 timing constraints に関する全体的な議論は、 FPGA内にある paths に関連していました。いよいよ FPGAの I/O portsの timing を制御する constraints のお話です。

ただし、 timing constraintsについて説明する前に、 FPGA と外部コンポーネントを同期するためのさまざまな方法について知っておく必要があります。このトピックを考慮せずに書かれた Timing constraints は価値がないかもしれません。さらに、 I/O インターフェイスを担当する logic が不適切に記述されている可能性があります。極端な場合、 PCB には、動作が保証されている I/O を可能にするために必要な配線がない場合があります。

外部コンポーネントとの同期を意識すれば、 timing constraintsに適した commands を選択できます。そのための実際的な側面については、次のページで説明します。

このページでは、 IOB registersについてご存知であることを前提としています。

Clock distribution

paths が FPGA内にある限り、 pathの両側の間にある clock skew を認識する必要はありません。 clockの分布はツールが担当し、 timing の計算では clock skew が考慮されました。

I/O timing constraintsの場合は異なります。 path の片側は、 FPGAの外部コンポーネントです。 data signalsと同期するために、このコンポーネントは pinsの 1 つで受信する clock に依存しています。しかし、この clock は何と同期していますか?

戦略は通常、次の 2 つのいずれかです。

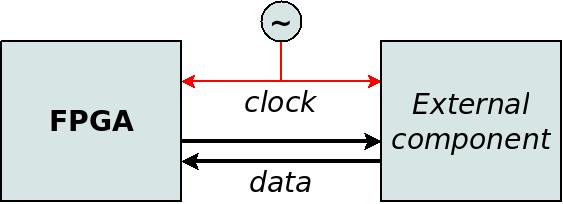

- System synchronous clock: 外部コンポーネントは、 FPGAの clock input pinと同じ clock signal に接続されます。この戦略は common clockとも呼ばれます。

- Source-synchronous clock: data signalsと一緒に特別な clock signal が提供されます。通常、 data signals は clockと同時に値を変更します。 rising edge または falling edgeのいずれかで。

これら 2 つの戦略については、次に詳しく説明します。 source-synchronous clock オプションに関しては、 data signals が inputs と outputsの場合、大きな違いがあります。したがって、これらのシナリオについては個別に説明します。

System synchronous clock

PCB で複数のコンポーネントを同期する最も簡単な方法は、すべてのコンポーネントを 1 つの clockに接続することです。これはsystem synchronous clock (またはcommon clock ) と呼ばれます。

この方法の利点は、すべてのコンポーネントの timing parameters が 1 つの clock signalに相対的であることです。したがって、 timing の計算を行うために、 clock は両側で同じになります。したがって、 PCB上の 2 つのコンポーネント間で伝播する data signal の場合、計算は FPGA内の path と同様になります。 path は、最初の clock edgeに相対的な clock-to-output で始まります。 pathの最後では、 tsu は 2 番目の clock edgeに相対的です。 system synchronous メソッドは、これら 2 つの clock edges が同じ clockに属することを意味します。

したがって、 system synchronous clock の操作は簡単ですが、この方法は比較的低い周波数にのみ適しています。 timing の計算の紹介で、最小の clock period は複数の timing parametersの合計であることを思い出してください。 最初の flip-flopの clock-to-output 、2 番目の flip-flopの propagation delay および tsu 。 output portの場合、 clock-to-output は比較的大きくなります。これは、 PCBのワイヤが必要な電圧に達するまでにかかる時間の長さだからです。しかし、それだけでは終わりません: clock skew および clock に関連するその他の不確実性も追加する必要があります。すべての数値を合計すると、最小限の clock period は印象的ではないかもしれません。

経験則として、 system synchronous clock は、 100 MHzより高い data rate の I/O には適していません。ただし、これは関係するコンポーネントによって大きく異なります。実際、一部の電子コンポーネントには、 frequenciesがはるかに低い場合でも、 system synchronous clockで満たすのが非常に難しい timing 要件があります。このようなコンポーネントは、 PCBを製造する前に I/O timing を計画することが重要である理由の 1 つです。

set_input_delay と set_output_delay (次のページで説明します) は、 system synchronous clockと組み合わせて使用するのに最適な timing constraints です。

Source-synchronous clock

多くの場合、 PCB 上の 2 つのコンポーネント間のインターフェースは、これらのコンポーネントの 1 つによって提供される clock に基づいています。当然、 clock が FPGA によって生成されるか、外部コンポーネントによって生成されるかによって違いが生じます。

したがって、4 つの関連するシナリオがあります。

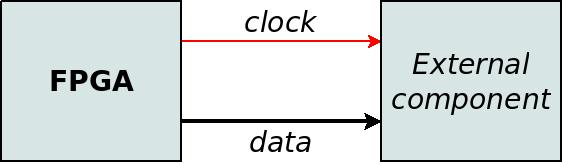

- data と clock は、 FPGAによって生成された outputs です。この比較的簡単なシナリオは、 source-synchronous outputsに関するページで個別に説明されています。

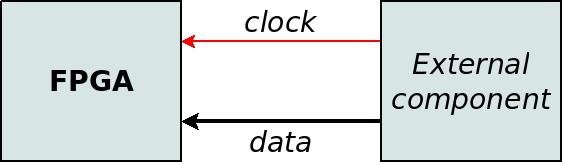

- data と clock は外部コンポーネントによって生成されます。したがって、 FPGA はこれらを input signalsとして受け取ります。 source-synchronous inputs に関するページは、このシナリオ専用です。

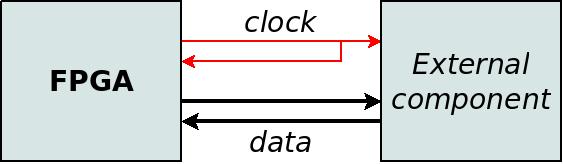

- clock は FPGAによって生成されますが、 data は双方向 (または inputs) です。これは source-synchronous inputsの特殊なケースです。 FPGA が clock を生成するという事実は、大きな違いはありません。 data inputs は、 PCB上の clock と同期されます。この clock は、 FPGAの内部に clock の関係で delay があります。このシナリオの詳細については、 source-synchronous outputsに関するページを参照してください。

- clock は外部コンポーネントによって生成され、 data は双方向です。 inputs から FPGAに関しては、これは data が外部コンポーネント (source-synchronous clock) によって生成されるシナリオに似ています。 FPGAの outputsに関しては、外部 clockと同期している output のように動作します。したがって、これらの outputs は system synchronousであるかのように配置されます。

Asynchronous inputs

一部の inputs は clockに関連付けられていません。たとえば、 pushbuttons、 I2C、 RS232 、および外部コンポーネントからのさまざまな status signals は、 clockと同期されません。これらの signals は通常、 FPGA内の clock よりもはるかに低速です。したがって、通常の解決策は、これらの signals を flip-flops (できればIOB registers ) でサンプリングし、通常の logic design 手法を続行することです。

これらの inputs は、サンプリングに使用される clock と同期していません。したがって、 IOB register (または portに接続された flip-flop ) はmetastability guardsの役割を果たします。したがって、 unrelated clocks間のclock domain crossingと同様に、 portごとに 2 番目の register を使用する必要があります。そうしないと、 input signals が遅く、現時点では design が適切に動作しているように見えても、予測不能で奇妙な動作が発生するリスクがあります。

timing constraints は、再現可能な動作を保証するように記述する必要があります。 flip-flops が IOB内に配置されていない場合でも、 IOB registersと同じガイドラインに従う必要があります。さらに安全を確保するには、これらの registersの役割に関連して、 metastability guards として専用の timing constraint を追加することもお勧めします (これについては別のページで説明されています)。

False paths

I/O ports のFalse paths は、原則として FPGA内の paths と同じです。 set_false_path command は、特定の portsに対して timing 要件が適用されないように要求するために使用されます。

False paths は、 FPGAの内部にある paths に関して既に説明されています。同じ理論的根拠に基づいて、 I/O ports の false paths の背後にある動機は、主に unconstrained pathsの空のリストを維持することです。間違いにより port に timing constraints がない場合に識別しやすくするために、このリストは空にする必要があります。

False paths は、 port の timing がまったく意味がない場合にのみ使用してください。たとえば、 LEDs と DIP switchesを使用します。

SDC constraintsの例:

set_false_path -to [get_ports led_0] set_false_path -from [get_ports dip_switch_0]

概要

このページでは、 FPGA と外部コンポーネントを同期させるためのいくつかの戦略について概説しました。選択した戦略は、 logic design だけでなく timing constraintsにも影響を与えます。

この知識があれば、 I/O timing constraintsの書き方について説明します。