多くの場合、すべての registers が I/O セルに入れられるようにして、 I/O timing を処理することを好みます。 timing が重要な場合、つまりです。

I/O register packing は Quartusのデフォルトではないようです。とにかく、このシナリオの怠け者のレシピは次のとおりです。

この投稿の以前のバージョンで、すべての I/Osで timing checking を無効にすることを提案しました。これにより、 implementation中に unconstrained path warning が沈黙し、特に、 Quartusのレポート ペインの「TimeQuest Timing Analyzer」セクションが赤くなるのを防ぎます。

set_false_path -from [get_ports] set_false_path -to [get_ports]

特に input portsに関しては、これはあまり良い考えではありません。これについては、以下でさらに詳しく説明します。

それにもかかわらず、 registers を I/O blockに入れるように fitter を説得する必要があります。 QSFでは、追加

set_instance_assignment -name FAST_OUTPUT_REGISTER ON -to * set_instance_assignment -name FAST_INPUT_REGISTER ON -to * set_instance_assignment -name FAST_OUTPUT_ENABLE_REGISTER ON -to *

これらの assignments をすべての registerに搭載するのはやや積極的ですが、うまくいきます。 fitter は I/O elements に対して warnings を発行し、これらの constraints を適用できません。これは実際には良いことです。

どれだけうまくいったかを見るには、 fitter report の "Resource Section" を調べ ( Quartusの reports paneで見つかる可能性があります)、"Input Registers" などを探してください。

その違いは、 I/O cellsを含む paths の timing reports で明らかです。たとえば、 I/O registerを含むこの path を比較します。

+----------------------------------------------------------------------------------+ ; Data Arrival Path ; +---------+---------+----+------+--------+-----------------------+-----------------+ ; Total ; Incr ; RF ; Type ; Fanout ; Location ; Element ; +---------+---------+----+------+--------+-----------------------+-----------------+ ; 2.918 ; 2.918 ; ; ; ; ; data path ; ; 0.000 ; 0.000 ; ; ; 1 ; DDIOOUTCELL_X3_Y0_N32 ; rst ; ; 0.465 ; 0.465 ; RR ; CELL ; 1 ; DDIOOUTCELL_X3_Y0_N32 ; rst|q ; ; 0.465 ; 0.000 ; RR ; IC ; 1 ; IOOBUF_X3_Y0_N30 ; RESETB~output|i ; ; 2.918 ; 2.453 ; RR ; CELL ; 1 ; IOOBUF_X3_Y0_N30 ; RESETB~output|o ; ; 2.918 ; 0.000 ; RR ; CELL ; 0 ; PIN_P3 ; RESETB ; +---------+---------+----+------+--------+-----------------------+-----------------+

DDIOOUTCELL 要素、および register と IOOBUFの間の routing 内の zero increment に注意してください。

比較のために、 I/O register が適用されなかった path を次に示します ( logicによって防止されたため)。

+--------------------------------------------------------------------------------+ ; Data Arrival Path ; +---------+---------+----+------+--------+-----------------+---------------------+ ; Total ; Incr ; RF ; Type ; Fanout ; Location ; Element ; +---------+---------+----+------+--------+-----------------+---------------------+ ; 8.284 ; 8.284 ; ; ; ; ; data path ; ; 0.000 ; 0.000 ; ; ; 1 ; FF_X3_Y0_N17 ; Dir_flop_sig ; ; 0.496 ; 0.496 ; RR ; CELL ; 8 ; FF_X3_Y0_N17 ; Dir_flop_sig|q ; ; 2.153 ; 1.657 ; RR ; IC ; 1 ; IOOBUF_X3_Y0_N9 ; DATA[7]~output|oe ; ; 8.284 ; 6.131 ; RF ; CELL ; 1 ; IOOBUF_X3_Y0_N9 ; DATA[7]~output|o ; ; 8.284 ; 0.000 ; FF ; CELL ; 1 ; PIN_T3 ; DATA[7] ; +---------+---------+----+------+--------+-----------------+---------------------+

ここでは、汎用 flip-flop がどのように信号を生成し、 routing delay が 1.657 nsになるかを示します。主な問題は、この routing delay が implementationごとに異なることです。したがって、ボードに signal integrity の問題がある場合、 FPGA design のバージョンが異なると問題が修正されるか、再発するように見えるため、 FPGA が原因である可能性があります。

Timing constraints

input ports も output ports も timing constraintsがタイトなはずなので、 I/O registersを最大限に活用する以外にそれらを満たすことはできません。目的の register packingで問題が発生した場合に timing failure が生成されるだけでなく、次に説明するように、最小限の input-to-register timingを実現する必要もあります。

以下の議論は、 registers を駆動する clock が外部の clock と直接関連している場合(つまり、 clock に整数を乗算する PLL など)にのみ適用されます。 registers を駆動する clock が外部の clockと実質的に関連していない場合、 この投稿で説明されているように、状況は大幅に複雑になります。

この問題を実証するには、次の Verilog codeを検討してください。

module top

(

input clk,

input in,

output reg out

);

reg in_d, in_d2;

wire pll_clk;

always @(posedge pll_clk)

begin

in_d <= in;

in_d2 <= in_d;

out <= in_d2;

end

/* Here comes an instantiation of a phase-compensating PLL, which

doesn't change the frequency */

endmodule

また、 SDC fileで次の constraint を検討してください。

create_clock -name main_clk -period 10 -waveform { 0 5 } [get_ports {clk}]

derive_pll_clocks

derive_clock_uncertainty

set_input_delay -clock main_clk -max 8.5 [get_ports in*]

set_input_delay -clock main_clk -min 0 [get_ports in*]

この投稿で説明されているように、 set_input_delay は信号源の最大値 delay であり、 clock から有効な logic stateまでの範囲です。 clockの時間周期は 10 nsに設定されているため、 delay constraint を 8.5 ns に設定すると、次の clock ( 10 ns)が到着するまで 1.5 ns が許容されます。言い換えれば、 FPGAのピンの setup time には constraint があり、 1.5 nsを超えないように強制されます。

この投稿で説明されているように、この目的には set_max_delay も使用できることに注意してください (場合によってはこれが唯一の方法です)。

これの compilation (上に示した FAST_INPUT_REGISTER ON QSF 割り当てと共に) は、 timing reportで次のセグメントを生成します。

+----------------------------------------------------------------------------------+

; Data Arrival Path ;

+---------+---------+----+------+--------+-------------------+---------------------+

; Total ; Incr ; RF ; Type ; Fanout ; Location ; Element ;

+---------+---------+----+------+--------+-------------------+---------------------+

; 0.000 ; 0.000 ; ; ; ; ; launch edge time ;

; 0.000 ; 0.000 ; ; ; ; ; clock path ;

; 0.000 ; 0.000 ; R ; ; ; ; clock network delay ;

; 8.500 ; 8.500 ; F ; iExt ; 1 ; PIN_F2 ; in ;

; 9.550 ; 1.050 ; ; ; ; ; data path ;

; 8.500 ; 0.000 ; FF ; IC ; 1 ; IOIBUF_X0_Y22_N15 ; in~input|i ;

; 9.308 ; 0.808 ; FF ; CELL ; 1 ; IOIBUF_X0_Y22_N15 ; in~input|o ;

; 9.308 ; 0.000 ; FF ; IC ; 1 ; FF_X0_Y22_N17 ; in_d|d ;

; 9.550 ; 0.242 ; FF ; CELL ; 1 ; FF_X0_Y22_N17 ; in_d ;

+---------+---------+----+------+--------+-------------------+---------------------+

output registerの場合とは異なり、リストに「DDIOINCELL」というタイプの flip-flop はありませんが、代わりに通常の flip-flop のように見えるものがあります。ただし、この flip-flop への配線には zero delay (赤でマーク) があることに注意してください。これは、 flip-flop と input buffer が融合されていることを明確に示しています。

この入力の datasheet report は次のように述べています。

+---------------------------------------------------------------------------------------------------+ ; Setup Times ; +-----------+------------+-------+-------+------------+---------------------------------------------+ ; Data Port ; Clock Port ; Rise ; Fall ; Clock Edge ; Clock Reference ; +-----------+------------+-------+-------+------------+---------------------------------------------+ ; in ; main_clk ; 1.282 ; 1.461 ; Rise ; altpll_component|auto_generated|pll1|clk[0] ; +-----------+------------+-------+-------+------------+---------------------------------------------+ +-----------------------------------------------------------------------------------------------------+ ; Hold Times ; +-----------+------------+--------+--------+------------+---------------------------------------------+ ; Data Port ; Clock Port ; Rise ; Fall ; Clock Edge ; Clock Reference ; +-----------+------------+--------+--------+------------+---------------------------------------------+ ; in ; main_clk ; -0.683 ; -0.862 ; Rise ; altpll_component|auto_generated|pll1|clk[0] ; +-----------+------------+--------+--------+------------+---------------------------------------------+

必要に応じて、 FPGA に必要な setup time は、 constraintによって設定された 1.5 ns 制限よりも低くなります。

次に、 input setup delay を 2 nsで緩め、他のすべてをそのままにして、 compilationを再実行します。

set_input_delay -clock main_clk -max 6.5 [get_ports in*]

set_input_delay -clock main_clk -min 0 [get_ports in*]

timing report のセグメントには、次のように記載されています。

+----------------------------------------------------------------------------------+

; Data Arrival Path ;

+---------+---------+----+------+--------+-------------------+---------------------+

; Total ; Incr ; RF ; Type ; Fanout ; Location ; Element ;

+---------+---------+----+------+--------+-------------------+---------------------+

; 0.000 ; 0.000 ; ; ; ; ; launch edge time ;

; 0.000 ; 0.000 ; ; ; ; ; clock path ;

; 0.000 ; 0.000 ; R ; ; ; ; clock network delay ;

; 6.500 ; 6.500 ; F ; iExt ; 1 ; PIN_F2 ; in ;

; 8.612 ; 2.112 ; ; ; ; ; data path ;

; 6.500 ; 0.000 ; FF ; IC ; 1 ; IOIBUF_X0_Y22_N15 ; in~input|i ;

; 7.308 ; 0.808 ; FF ; CELL ; 1 ; IOIBUF_X0_Y22_N15 ; in~input|o ;

; 8.370 ; 1.062 ; FF ; IC ; 1 ; FF_X0_Y22_N17 ; in_d|d ;

; 8.612 ; 0.242 ; FF ; CELL ; 1 ; FF_X0_Y22_N17 ; in_d ;

+---------+---------+----+------+--------+-------------------+---------------------+

は?インターコネクトが急に 1.062 nsに上がった?! register の配置は変わっていないので、 in_d が I/O registerであることは間違いありません。では、この遅れはどこから来たのでしょうか。

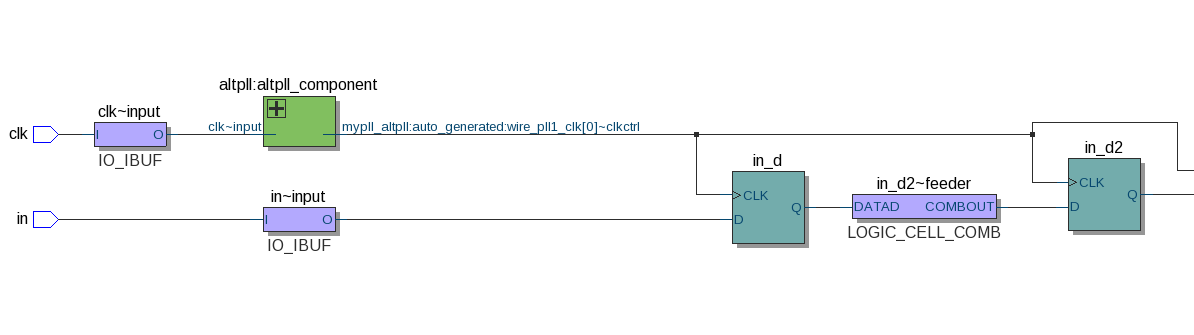

これに答えるには、 design を詳しく調べる必要があります。完全な compilation と Tools > Netlist Viewers > Technology Map Viewer (Post-Fitting)を選択すると、次の diagram が表示されます (下に部分的に表示されています。クリックして拡大します)。

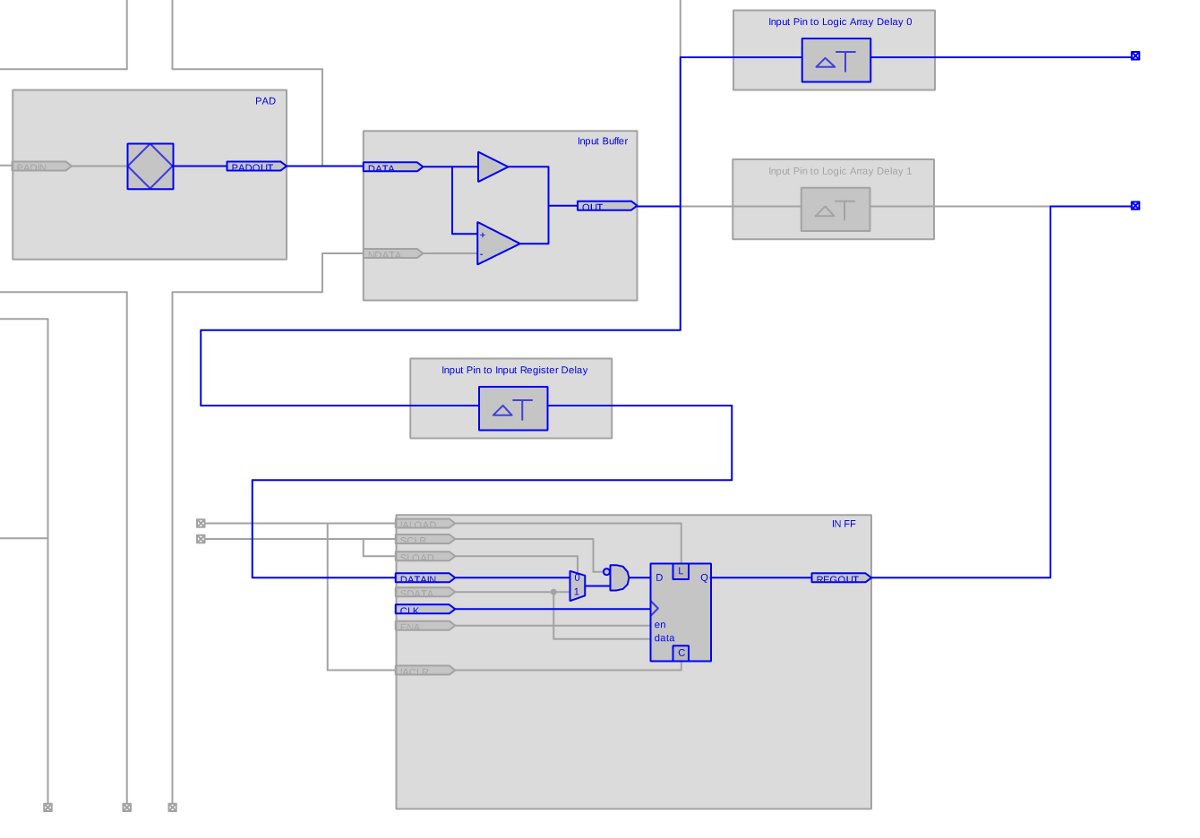

in_d ( register) を右クリックして Locate Note > Locate in Resource Property Editor を選択すると、次のように表示されます (クリックして拡大)。

この図面の右側 (上には表示されていません) では、プロパティ "Input Pin to Input Register Delay" が 2に設定されています。これが delayの理由です。 constraint を緩める前は 0にしました。直接の教訓は次のとおりです。

setup constraint がテクノロジーの可能な限り最高の値に設定されていない場合、 Quartus はその費用で delay を追加する可能性があります。

しかし、なぜ、 Quartus、なぜですか?

したがって、 Quartus が input pad と registerの間にこの delay を挿入する理由が不思議に思われるかもしれません。できるだけ早くサンプリングすることがポイントではありませんでしたか?これに答えるために、更新された datasheet reportを見てみましょう。

---------------------+ ; Data Port ; Clock Port ; Rise ; Fall ; Clock Edge ; Clock Reference ; +-----------+------------+-------+-------+------------+---------------------------------------------+ ; in ; main_clk ; 2.205 ; 2.523 ; Rise ; altpll_component|auto_generated|pll1|clk[0] ; +-----------+------------+-------+-------+------------+---------------------------------------------+ +-----------------------------------------------------------------------------------------------------+ ; Hold Times ; +-----------+------------+--------+--------+------------+---------------------------------------------+ ; Data Port ; Clock Port ; Rise ; Fall ; Clock Edge ; Clock Reference ; +-----------+------------+--------+--------+------------+---------------------------------------------+ ; in ; main_clk ; -1.570 ; -1.882 ; Rise ; altpll_component|auto_generated|pll1|clk[0] ; +-----------+------------+--------+--------+------------+---------------------------------------------+

2 ns が delay constraintから削減されたことを思い出してください。したがって、最大許容 setup time は 1.5 ns から 3.5 nsに上がりました。 slack がほぼ 1 nsであることから、この要件が満たされていることは容易にわかります。

Quartus は、「 setup の要件は、 2 nsの余剰分で簡単に満たすことができます。 1 ns を setup timeに追加し、 1 ns を hold time requirement (つまり 0 ns) に追加しましょう」と言いました。実際、この delayに 1.062 ns を追加することで、 hold time は -0.683 ns から -1.570 ns に改善されました (違いが正確ではない理由について私を責めないでください)。

結論: Quartus は、 setup と holdの両方のマージンを広げ、 jitterに対する入力をより堅牢にしました。これはかなり賢明なことですが、多くの場合、これは望ましくなく、期待もされていません。

結論: input から registerへと絶対に最小限の delay を取得したい場合は、失敗した delay constraint で compilation を実行し、この失敗を解決するのに十分なだけ constraint を緩めます。これにより、 Quartus が、より優れた hold timeのためにこの input delay を追加することによって、 timing を「改善」しようとしないことが保証されます。

DDR primitivesの使用

Intelの FPGAs には I/O cells 上またはその近くに logic があり、出力の生成とダブル clock rateでの入力のサンプリングを可能にします。このトピックについては、関連するユーザー ガイド ug_altddio.pdfで詳しく説明されています。 DDR primitive をインスタンス化する (または ALTDDIO_BIDIR megafunctionを使用する) ことは、ツールに registers を I/O cellsに強制的に配置させる魅力的な方法です。ただし、これは必ずしも良い考えではありません。

たとえば、次のような instantiation :

altddio_bidir ioddr ( .padio(pin), .aclr (1'b0), .datain_h(datain_h), .datain_l(datain_l), .inclock(clk), .oe(oe), .outclock(clk), .dataout_h(dataout_h), .dataout_l(dataout_l), .oe_out (), .aset (1'b0), .combout(), .dqsundelayedout(), .inclocken(1'b1), .outclocken(1'b1), .sclr(1'b0), .sset(1'b0)); defparam ioddr.extend_oe_disable = "OFF", ioddr.implement_input_in_lcell = "OFF", ioddr.intended_device_family = "Cyclone IV E", ioddr.invert_output = "OFF", ioddr.lpm_hint = "UNUSED", ioddr.lpm_type = "altddio_bidir", ioddr.oe_reg = "REGISTERED", ioddr.power_up_high = "OFF", ioddr.width = 1;

これは確かに、双方向の DDR インターフェイスを実装する logic になりますが、 timing に関する限り、少なくとも Cyclone IVでは部分的に成功しています。 clock-to-output timing は、 I/O cellにパックされているプレーンな output register とまったく同じですが、 input path の遅延は、実際には上記の instantiation で悪化しています。他の Intel FPGA ファミリでは結果が異なる場合があります。

DDR primitiveでプレーンな SDR registers を模倣するには、その datain_h ポートと datain_l ポートを同じワイヤに接続する必要があるため、 clockの falling edge は何も変更しないことに注意してください。同様に、 falling edgeでサンプリングされるため、 dataout_l ポートの値は無視する必要があります。また、 output enable port (oe) は SDR input であることに注意してください。私の知る限り、 high-Z を Intel FPGAsで DDR rate とオン/オフすることはできません。少なくとも、付属の logic primitivesではそうではありません。

入力ではなく、 output registersでうまく機能した理由は次のとおりです。 ヒントは上記の timing reports にあります。 プレーンな I/O cell registerでも、 DDIOOUTCELL_Xn_Ym_Nk コンポーネントは registerとして使用されます。つまり、 DDR output register は single-rate outputsでも使用されますが、 clock edgeは 1 つだけです。 input pathについては、上記の timing reports は logic fabric register (FF_Xn_Ym_Nk) が使用されていることを示しています。そして、ここに核心があります: DDR input logic は logic fabric にも実装されています。さらに悪いことに、 DDRの場合、 combinatorial blocks は I/O cell と flip-flop の間に挟まれます。率直に言って、その理由がわかりません。そのような combinatorial block はそれぞれ、単一の入力から単一の出力への単なるパススルーだからです。

これらの観察結果は、 timing reports だけでなく、 Quartusの Post-Fit Technology Map Viewerによって表示される図面によって裏付けられています。特に、それらの役に立たない combinatorial blocks は、これらの情報源で明らかです。

この問題全体は、 FPGA family ごとに異なる可能性があります。 Cyclone IVに関しては、出力に DDR primitives を使用することだけが理にかなっています。

さらに重要なことは、 output register が必要なときに DDR primitive output が使用されるという事実により、他の出力に合わせた output clock を生成できることです。これを実現するには、 datain_h ポートと datain_l ポートでそれぞれ一定の '1' と '0' を DDR output primitive に供給します。その他の出力については、 output register パッキングを使用する必要があります。したがって、他の出力のトグルは、 DDR outputから派生した clock の rising edge に合わせられます。

よくほとんど。 output clock の timing analysis は異なります。 clock は、2 つの output registers のどちらが出力をフィードするかを選択する mux をトグルするためです (詳細については、水平方向にスクロールします)。

+------------------------------------------------------------------------------------------------------------------------------------+

; Data Arrival Path ;

+---------+---------+----+------+--------+-------------------------+-----------------------------------------------------------------+

; Total ; Incr ; RF ; Type ; Fanout ; Location ; Element ;

+---------+---------+----+------+--------+-------------------------+-----------------------------------------------------------------+

; 0.000 ; 0.000 ; ; ; ; ; launch edge time ;

; 0.000 ; 0.000 ; ; ; ; ; clock path ;

; 0.000 ; 0.000 ; R ; ; ; ; clock network delay ;

; 0.000 ; 0.000 ; R ; ; 1 ; PIN_B12 ; osc_clock ;

; 5.610 ; 5.610 ; ; ; ; ; data path ;

; 0.000 ; 0.000 ; RR ; IC ; 1 ; IOIBUF_X19_Y29_N8 ; osc_clock~input|i ;

; 0.667 ; 0.667 ; RR ; CELL ; 2 ; IOIBUF_X19_Y29_N8 ; osc_clock~input|o ;

; 0.853 ; 0.186 ; RR ; IC ; 1 ; CLKCTRL_G12 ; osc_clock~inputclkctrl|inclk[0] ;

; 0.853 ; 0.000 ; RR ; CELL ; 165 ; CLKCTRL_G12 ; osc_clock~inputclkctrl|outclk ;

; 1.971 ; 1.118 ; RR ; IC ; 1 ; DDIOOUTCELL_X16_Y29_N11 ; sram_controller_ins|ddr_clk|auto_generated|ddio_outa[0]|muxsel ;

; 3.137 ; 1.166 ; RR ; CELL ; 1 ; DDIOOUTCELL_X16_Y29_N11 ; sram_controller_ins|ddr_clk|auto_generated|ddio_outa[0]|dataout ;

; 3.137 ; 0.000 ; RR ; IC ; 1 ; IOOBUF_X16_Y29_N9 ; sram_clk~output|i ;

; 5.610 ; 2.473 ; RR ; CELL ; 1 ; IOOBUF_X16_Y29_N9 ; sram_clk~output|o ;

; 5.610 ; 0.000 ; RR ; CELL ; 0 ; PIN_E10 ; sram_clk ;

+---------+---------+----+------+--------+-------------------------+-----------------------------------------------------------------;

これは register-to-pin 分析ではなく、 clock-to-pin分析であることに注意してください。ただし、 set_output_delay constraint にはこの path が含まれます。ただし、 registers から portsまでの set_max_delay constraint を使用する場合、この pathは含まれないため、個別に処理する必要があります。つまり、 set_max_delay を使用する場合は、次の形式にする必要があります。

set_max_delay -from [get_clocks main_clk] -to [get_ports sram_clk] 3.8

これを、 registerのみで駆動される、同じ voltage standard などを備えた別の pin と比較します。

+----------------------------------------------------------------------------------------------------------------------+ ; Data Arrival Path ; +---------+---------+----+------+--------+-------------------------+---------------------------------------------------+ ; Total ; Incr ; RF ; Type ; Fanout ; Location ; Element ; +---------+---------+----+------+--------+-------------------------+---------------------------------------------------+ ; 0.000 ; 0.000 ; ; ; ; ; launch edge time ; ; 2.507 ; 2.507 ; ; ; ; ; clock path ; ; 0.000 ; 0.000 ; ; ; ; ; source latency ; ; 0.000 ; 0.000 ; ; ; 1 ; PIN_B12 ; osc_clock ; ; 0.000 ; 0.000 ; RR ; IC ; 1 ; IOIBUF_X19_Y29_N8 ; osc_clock~input|i ; ; 0.667 ; 0.667 ; RR ; CELL ; 2 ; IOIBUF_X19_Y29_N8 ; osc_clock~input|o ; ; 0.853 ; 0.186 ; RR ; IC ; 1 ; CLKCTRL_G12 ; osc_clock~inputclkctrl|inclk[0] ; ; 0.853 ; 0.000 ; RR ; CELL ; 165 ; CLKCTRL_G12 ; osc_clock~inputclkctrl|outclk ; ; 1.970 ; 1.117 ; RR ; IC ; 1 ; DDIOOUTCELL_X37_Y29_N11 ; sram_controller_ins|dq_wr_data[6]|clk ; ; 2.507 ; 0.537 ; RR ; CELL ; 1 ; DDIOOUTCELL_X37_Y29_N11 ; sram_controller:sram_controller_ins|dq_wr_data[6] ; ; 5.645 ; 3.138 ; ; ; ; ; data path ; ; 2.717 ; 0.210 ; ; uTco ; 1 ; DDIOOUTCELL_X37_Y29_N11 ; sram_controller:sram_controller_ins|dq_wr_data[6] ; ; 3.182 ; 0.465 ; RR ; CELL ; 1 ; DDIOOUTCELL_X37_Y29_N11 ; sram_controller_ins|dq_wr_data[6]|q ; ; 3.182 ; 0.000 ; RR ; IC ; 1 ; IOOBUF_X37_Y29_N9 ; sram_dq[6]~output|i ; ; 5.645 ; 2.463 ; RR ; CELL ; 1 ; IOOBUF_X37_Y29_N9 ; sram_dq[6]~output|o ; ; 5.645 ; 0.000 ; RR ; CELL ; 1 ; PIN_G14 ; sram_dq[6] ; +---------+---------+----+------+--------+-------------------------+---------------------------------------------------;

clock-to-output の合計時間は、後者の path は表面上は完全に異なりますが、 35 psを超える差はありません。これは偶然ではありません。 FPGA は、この類似性を生み出すように明確に設計されています。具体的には、上記の timing analysis は 100°Cの温度での slow 1200 mV ですが、この小さな違いは他の分析条件でも一貫しています。