소개

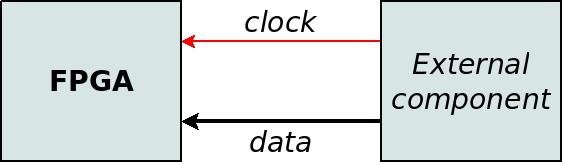

이 페이지에서는 source-synchronous data inputs에 대해 설명합니다. 이 기술은 data inputs가 외부 구성 요소가 이러한 inputs와 병렬로 생성하는 clock 와 동기화됨을 의미합니다.

이 방법은 단순히 외부 구성 요소가 작동하는 방식이기 때문에 종종 사용됩니다. 또 다른 좋은 이유는 data 의 소스가 FPGA에서 물리적으로 멀리 떨어져 있기 때문입니다. FPGA 와 다른 쪽 사이에 케이블과 커넥터가 있을 수도 있습니다. 예를 들어, pixel data를 전송하는 digital camera 입니다.

source-synchronous clock 의 가능한 어려움은 항상 활성화되지 않을 수 있다는 것입니다. clock signal은 매달린 물리적 연결이나 과도한 소음의 영향을 받을 수도 있습니다. clock 에 안정적인 clock period가 없거나 jitter가 지나치게 높을 수도 있습니다. 이는 data (따라서 clock)의 소스가 microprocessor의 I/O peripheral일 때 자주 발생합니다.

일반적으로 clock 와 data 사이의 관계를 설명하는 별도의 페이지가 있습니다.

불안정한 clock에 대처하기

source-synchronous inputs 에서 가장 중요한 지침은 clock을 FPGA내부의 logic elements 에 직접 연결해서는 안된다는 것입니다. 오히려 FPGA 내부에서 사용되는 clock은 FPGA내부에 있는 PLL 에서 생성된 깨끗한 clock여야 합니다.

외부 clock이 FPGA내부의 logic 에 직접 연결되면 이상한 문제가 발생할 수 있습니다. 불량한 clock은 clock의 문제처럼 보이지 않는 예상치 못한 동작을 생성합니다. 과도한 jitter 및 glitches는 design의 안정적인 작동을 보장하는 timing 요구 사항을 위반할 수 있습니다. 결과적으로 Verilog code에 따르면 불가능한 상황을 포함하여 사실상 모든 일이 발생할 수 있습니다. 따라서 문제가 FPGA design의 bug 라고 잘못 생각하기 쉽습니다.

clock 의 문제로 인해 clock cycles만 손실되고 결과적으로 일부 data 요소가 누락될 것이라고 (잘못) 생각하는 것은 당연합니다. 나쁜 clock이 다른 문제를 일으킬 때, 이 문제를 해결하려는 시도는 종종 logic design 에서 가장 관련이 있어 보이는 부분에 집중됩니다. 그것은 많은 시간을 낭비할 수 있습니다.

외부 clock을 logic fabric 에서 직접 사용할 수 있는 유일한 상황은 이 clock이 안정적이고 깨끗할 때입니다. FPGA가 작동하기 시작할 때 이 clock이 안정적이지 않으면 이 문제를 치료해야 합니다. clock이 불안정한 이상 이 clock에 의존하는 logic 에 reset을 적용해야 한다.

가능한 전략

외부 clock와의 동기화에는 주로 네 가지 가능한 전략이 있습니다. 이러한 전략은 특별한 순서 없이 아래에서 설명합니다.

전략 #1: 01-signal sampling

이 전략은 source-synchronous inputs의 가장 강력한 방법입니다. 외부 clock이 오작동하는 경우 01-signal sampling은 다른 방법보다 확실한 이점을 갖습니다. 그러나 이 방법은 데이터 소스의 clock 의 빈도가 상대적으로 낮은 경우에만 유용합니다.

이 방법은 전용 페이지에서 별도로 논의 됩니다.

전략 #2: PLL사용

이 전략을 사용하면 외부 clock이 FPGA에 있는 PLL 의 input 에 연결됩니다. 이 PLL의 output clock은 logic elements에 사용됩니다. PLL이 잠기지 않은 경우 이러한 logic elements 에 reset signal이 적용됩니다. 이 솔루션은 logic elements가 안정적인 clock에 의존하도록 합니다. PLL의 output clock이 안정적이지 않으면 reset이 logic elements를 비활성화합니다.

PLL은 외부 clock을 직접 연결하는 것에 비해 timing constraints를 구현하기가 더 쉽습니다. PLL은 clock pin 와 FPGA의 내부 clock사이에서 delay을 보완합니다.

그러나 외부 clock 의 결함으로 인해 PLL의 output에서 과도한 jitter가 발생할 수 있습니다. PLL의 lock detector는 PLL이 생산하는 clock이 비정상적으로 시끄럽더라도 계속해서 PLL이 제대로 작동함을 나타낼 수 있습니다. 이 상황에 대한 간단한 해결책은 없습니다. 한 가지 가능성은 PLL의 output에 의존하는 logic을 위해 timing constraints를 바꾸는 것이다. 예를 들어, timing constraints 에 있는 clock의 jitter는 PLL이 초과하지 않을 값으로 증가할 수 있습니다( loss of lock가 발생하기 때문).

이 전략과 system synchronous clocking 사이에는 유사점이 있습니다. 두 시나리오 모두에서 외부 clock은 PLL에 연결되고 이 PLL 의 output은 FPGA내부에서 사용됩니다. 따라서 timing constraints는 system synchronous clock 와 같은 방식으로 작성됩니다.

PLL은 일반적으로system synchronous clock에 최적인 방식으로 output clock을 external clock 와 정렬합니다. source synchronous clock 의 최적 정렬은 약간 다를 수 있습니다. 두 가능성 모두에서 clocks는 완벽하게 정렬되지 않았습니다. 오히려 clocks의 edges사이에는 의도적으로 약간의 시차가 있습니다. 이 시차를 통해 I/O registers의 timing 요구 사항을 더 쉽게 충족할 수 있습니다. 일부 PLLs는 최적의 성능을 위해 clocks를 source synchronous clock와 정렬하도록 구성할 수 있습니다.

이 전략은 여기에 나열된 다른 전략과 비교하여 구현하기 가장 쉬운 전략입니다. 비교적 높은 clock 주파수에 적합합니다. 그러나 I/O가 할 수 있는 최대 주파수에 가까운 주파수의 경우 이 전략이 작동하지 않을 수 있습니다.

전략 #3: Phase shifting

이 전략은 일반적으로 data rate가 FPGA가 지원할 수 있는 최대값에 근접할 때 선택됩니다.

timing requirements가 해당 data rates에서 작동하지 않음을 보장하는 일반적인 방법은 다음과 같습니다. timing constraints를 달성하는 것은 불가능합니다. 그러나 data signals 의 안정적인 샘플링은 여전히 가능합니다.

timing constraints 의 문제점은 계산을 통해 timing requirements를 보장하는 것입니다. 이러한 계산에는 몇 가지 불확실한 매개변수(예: FPGA제조의 차이)가 포함됩니다. 이러한 매개변수를 고려하면 계산 시 신뢰할 수 있는 샘플링을 보장하는 timing 솔루션이 생성되지 않습니다. data rate가 매우 높으면 이러한 불확실성에 낭비할 timing 잉여가 없습니다.

하지만 특정 FPGA chip의 경우 이러한 매개변수는 일정합니다. 따라서 해결책은 FPGA가 작동하는 동안 올바른 timing을 검색하는 것입니다. 실제로 이는 FPGA 내부의 state machine이 data clock 와 sampling의 순간 사이에서 delay을 조정한다는 것을 의미합니다. 따라서 계산에 의존하기보다는 적응 메커니즘을 사용하여 최적의 timing을 찾습니다. 이 메커니즘을 phase shifting 라고 합니다.

이 전략은 종종 DDR SDRAM memories의 data signals 에서 사용됩니다. 이 애플리케이션에서 목표는 항상 가능한 한 높은 data rate 에 도달하는 것입니다. 따라서 I/O ports의 기능은 한계까지 밀려납니다. 따라서 phase shifting은 data inputs가 안정적으로 샘플링되도록 보장하는 유일한 방법입니다. DDR memory가 초기화된 후 data 의 특수 시퀀스가 memory 에 기록됩니다( data signals 에서 memory는 source-synchronous outputs 이므로 timing에는 어려움이 없습니다). 그런 다음 FPGA는 DDR memory의 동일한 부분에서 반복해서 읽습니다. state machine은 샘플링의 delay을 점진적으로 변경하여 최적의 timing을 찾습니다. 예상되는 input data는 이전에 작성된 data 와 동일한 시퀀스이기 때문에 알려져 있습니다. 따라서 state machine은 data 의 신뢰성을 쉽게 평가하고 최적의 delay을 찾을 수 있습니다.

이 메커니즘의 흥미로운 특징은 DDR chip 에서 제공되는 data clock을 무시할 수 있다는 것입니다. DDR memory는 FPGA가 생성하는 clock 와 동기화됩니다. 이 clock은 DDR memory가 수신하는 source-synchronous outputs 의 일부입니다. 따라서 source-synchronous inputs 의 data clock이 FPGA에서 생성되는 clock 와 정확히 동일한 주파수를 갖는다는 것이 보장됩니다. 따라서 phase shifting 메커니즘은 data와 함께 제공되는 clock 대신 내부 clock 에 의존할 수 있습니다. 이 두 clocks사이에 알려지지 않은 delay이 있다는 것은 중요하지 않습니다. state machine은 이 delay와 관계없이 최적의 timing을 찾습니다.

실제로 DDR memories에서 이 메커니즘이 일반적으로 구현되는 방식은 다음과 같습니다. DDR memories 에 source-synchronous clock ( data strobe라고 함)가 있지만 phase shifting 메커니즘의 일반적인 구현은 이 signal을 무시합니다. 그 근거는 strobe와 정렬하는 것보다 data signals가 안정적으로 도착하는지 확인하는 것이 더 중요하다는 것입니다.

따라서 phase shifting을 사용하면 data clock이 필요하지 않습니다. 내부 clock은 주파수가 data rate와 정확히 동일한 것으로 보장되는 경우 대신 사용할 수 있습니다.

이 전략에서 timing constraints 의 목적은 일반 IOB registers 와 동일합니다.

전략 #4: clock 직접 사용

이 전략은 분명히 가장 간단한 것입니다. 외부 clock은 FPGA내부의 flip-flops 에 직접 연결됩니다. 이 같은:

module top (

input data_clk,

input [7:0] data

);

reg [7:0] data_samp;

always @(posedge data_clk)

begin

data_samp <= data;

[ ... ]

end

위에서 언급했듯이 이 전략은 일반적으로 좋은 생각이 아닙니다. 주된 이유는 @data_clk 에 glitch가 있으면 이 clock 에 의존하는 모든 logic이 예측 불가능 해지기 때문입니다.

깨끗하고 안정적이라고 보장된다면 이런 방식으로 외부 clock을 사용하는 것이 합리적일 수 있습니다. 하지만 이것이 보장된다 하더라도 clock pin 와 flip-flops사이에 delay이 있기 때문에 timing requirements를 달성하기 어려울 수 있습니다. 일부 FPGAs는 이 delay을 줄이기 위해 특별한 clock resources를 가지고 있습니다. 이를 위해 전용 clock input pin을 사용하고 I/O ports를 FPGA의 특정 영역으로 제한해야 할 수도 있습니다.

clock을 직접 사용하는 경우 timing constraints는 system synchronous clock 와 동일한 방식으로 작성됩니다.

이 전략에 대한 간단한 대안은 위에서 제안한 대로 PLL을 사용하는 것입니다. data clock이 안정적이지 않으면 01-signal sampling을 고려해야 합니다.

요약

이 페이지에서 01-signal sampling이 먼저 언급되고 이 전략이 별도의 페이지 에 설명되어 있는 것은 우연이 아닙니다. 이것은 data rate가 이 방법이 할 수 있는 것보다 높지 않은 경우 가장 권장되는 방법입니다.

다른 전략을 고려한다면 data clock의 안정성에 주목하는 것이 중요하다. clock이 허용된 동작(예: clock period 및 최대 jitter)에서 벗어나는 경우 관련 logic의 영구적이고 복구 불가능한 오작동이 발생할 수 있습니다. reset 만이 logic을 정상 작동 상태로 되돌립니다.

신뢰할 수 있는 clock을 생성하기 위해 PLL을 사용하면 상황이 상당히 개선됩니다. PLL의 output은 lock detector이 나타내는 한 신뢰할 수 있습니다. 그렇지 않으면 이 logic 에 reset을 적용해야 합니다.